全部

▼

搜索

熱搜:

位置:中冶有色 >

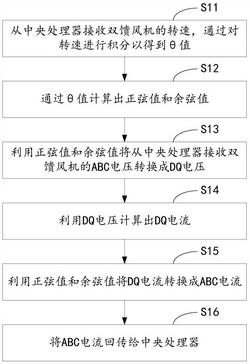

> 基于FPGA的雙饋風(fēng)機(jī)的建模方法及其系統(tǒng)

191

編輯:管理員

來(lái)源:上海科梁信息工程股份有限公司

191

編輯:管理員

來(lái)源:上海科梁信息工程股份有限公司

分享 0

分享 0

舉報(bào) 0

舉報(bào) 0

收藏 0

收藏 0

反對(duì) 0

反對(duì) 0

點(diǎn)贊 0

點(diǎn)贊 0

中冶有色技術(shù)平臺(tái)

中冶有色技術(shù)平臺(tái) 2025年03月25日 ~ 27日

2025年03月25日 ~ 27日  2025年03月28日 ~ 30日

2025年03月28日 ~ 30日  2025年03月29日 ~ 31日

2025年03月29日 ~ 31日  2025年04月11日 ~ 13日

2025年04月11日 ~ 13日